**IEEE**

## IEEE Standard Format for LSI-Package-Board Interoperable Design

**IEEE Computer Society**

Sponsored by the Design Automation Standards Committee

IEEE 3 Park Avenue New York, NY 10016-5997 USA

IEEE Std 2401™-2015

# IEEE Standard Format for LSI-Package-Board Interoperable Design

Sponsor

Design Automation Standards Committee of the IEEE Computer Society

Approved 3 September 2015

**IEEE-SA Standards Board**

#### **Copyrights and Permissions**

The following figures are reprinted with permission from JEITA<sup>1</sup>

Figure i, Figure i, Figure 1, Figure 3, Figure 16, Figure 17, Figure 18, Figure 19, Figure 20, Figure 21, Figure 22, Figure 23, Figure 24, Figure 25, Figure 26, Figure 27, Figure 28, Figure 29, Figure 30, Figure 31, Figure 32, Figure 33, Figure 34, Figure 35, Figure 36, Figure 37, Figure 38, Figure 39, Figure 40, Figure 41, Figure 42, Figure 43, Figure 44, Figure 45, Figure 46, Figure 47, Figure 48, Figure 49, Figure 50, Figure 51, Figure 60, Figure 61, Figure 62, Figure 63, Figure B.1, Figure B.3, Figure B.5, Figure B.6, Figure B.7, Figure B.8, Figure B.10, Figure B.11, Figure B.12, Figure B.13, Figure B.14, Figure B.15, Figure B.16, Figure B.17, Figure B.18, Figure B.19, Figure B.20, Figure B.21, Figure B.22, Figure B.23, Figure B.24, Figure B.25, Figure B.26, Figure B.27, Figure B.28, Figure B.29

**Abstract:** A method is provided for specifying a common interoperable format for electronic systems design. The format provides a common way to specify information/data about the project management, netlists, components, design rules, and geometries used in Large-Scale Integrated Circuit-Package-Board designs. The method provides the ability to make electronic systems a key consideration early in the design process; design tools can use it to exchange information/data seamlessly.

**Keywords:** common interoperable format, components, design analysis, design rules, geometries, IEEE 2401<sup>™</sup>, large-scale integrated circuits, netlists, packages for LSI circuits, printed circuit board, project management, Verilog-HDL

The Institute of Electrical and Electronics Engineers, Inc. 3 Park Avenue, New York, NY 10016-5997, USA

Copyright © 2015 by The Institute of Electrical and Electronics Engineers, Inc. All rights reserved. Published 18 December 2015. Printed in the United States of America.

IEEE is a registered trademark in the U.S. Patent & Trademark Office, owned by The Institute of Electrical and Electronics Engineers, Incorporated.

PDF: ISBN 978-0-7381-9913-9 STD20368 Print: ISBN 978-0-7381-9914-6 STDPD20368

IEEE prohibits discrimination, harassment, and bullying.

For more information, visit http://www.ieee.org/web/aboutus/whatis/policies/p9-26.html.

No part of this publication may be reproduced in any form, in an electronic retrieval system or otherwise, without the prior written permission of the publisher.

<sup>&</sup>lt;sup>1</sup> Every effort has been made to secure permission to reprint borrowed material contained in this document. If omissions have been made, please bring them to our attention.

#### Important Notices and Disclaimers Concerning IEEE Standards Documents

IEEE documents are made available for use subject to important notices and legal disclaimers. These notices and disclaimers, or a reference to this page, appear in all standards and may be found under the heading "Important Notice" or "Important Notices and Disclaimers Concerning IEEE Standards Documents."

## Notice and Disclaimer of Liability Concerning the Use of IEEE Standards Documents

IEEE Standards documents (standards, recommended practices, and guides), both full-use and trial-use, are developed within IEEE Societies and the Standards Coordinating Committees of the IEEE Standards Association ("IEEE-SA") Standards Board. IEEE ("the Institute") develops its standards through a consensus development process, approved by the American National Standards Institute ("ANSI"), which brings together volunteers representing varied viewpoints and interests to achieve the final product. Volunteers are not necessarily members of the Institute and participate without compensation from IEEE. While IEEE administers the process and establishes rules to promote fairness in the consensus development process, IEEE does not independently evaluate, test, or verify the accuracy of any of the information or the soundness of any judgments contained in its standards.

IEEE does not warrant or represent the accuracy or content of the material contained in its standards, and expressly disclaims all warranties (express, implied and statutory) not included in this or any other document relating to the standard, including, but not limited to, the warranties of: merchantability; fitness for a particular purpose; non-infringement; and quality, accuracy, effectiveness, currency, or completeness of material. In addition, IEEE disclaims any and all conditions relating to: results; and workmanlike effort. IEEE standards documents are supplied "AS IS" and "WITH ALL FAULTS."

Use of an IEEE standard is wholly voluntary. The existence of an IEEE standard does not imply that there are no other ways to produce, test, measure, purchase, market, or provide other goods and services related to the scope of the IEEE standard. Furthermore, the viewpoint expressed at the time a standard is approved and issued is subject to change brought about through developments in the state of the art and comments received from users of the standard.

In publishing and making its standards available, IEEE is not suggesting or rendering professional or other services for, or on behalf of, any person or entity nor is IEEE undertaking to perform any duty owed by any other person or entity to another. Any person utilizing any IEEE Standards document, should rely upon his or her own independent judgment in the exercise of reasonable care in any given circumstances or, as appropriate, seek the advice of a competent professional in determining the appropriateness of a given IEEE standard.

IN NO EVENT SHALL IEEE BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO: PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE PUBLICATION, USE OF, OR RELIANCE UPON ANY STANDARD, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE AND REGARDLESS OF WHETHER SUCH DAMAGE WAS FORESEEABLE.

#### Translations

The IEEE consensus development process involves the review of documents in English only. In the event that an IEEE standard is translated, only the English version published by IEEE should be considered the approved IEEE standard.

### **Official statements**

A statement, written or oral, that is not processed in accordance with the IEEE-SA Standards Board Operations Manual shall not be considered or inferred to be the official position of IEEE or any of its committees and shall not be considered to be, or be relied upon as, a formal position of IEEE. At lectures, symposia, seminars, or educational courses, an individual presenting information on IEEE standards shall make it clear that his or her views should be considered the personal views of that individual rather than the formal position of IEEE.

### Comments on standards

Comments for revision of IEEE Standards documents are welcome from any interested party, regardless of membership affiliation with IEEE. However, IEEE does not provide consulting information or advice pertaining to IEEE Standards documents. Suggestions for changes in documents should be in the form of a proposed change of text, together with appropriate supporting comments. Since IEEE standards represent a consensus of concerned interests, it is important that any responses to comments and questions also receive the concurrence of a balance of interests. For this reason, IEEE and the members of its societies and Standards Coordinating Committees are not able to provide an instant response to comments or questions except in those cases where the matter has previously been addressed. For the same reason, IEEE does not respond to interpretation requests. Any person who would like to participate in revisions to an IEEE standard is welcome to join the relevant IEEE working group.

Comments on standards should be submitted to the following address:

Secretary, IEEE-SA Standards Board 445 Hoes Lane Piscataway, NJ 08854 USA

#### Laws and regulations

Users of IEEE Standards documents should consult all applicable laws and regulations. Compliance with the provisions of any IEEE Standards document does not imply compliance to any applicable regulatory requirements. Implementers of the standard are responsible for observing or referring to the applicable regulatory regulatory requirements. IEEE does not, by the publication of its standards, intend to urge action that is not in compliance with applicable laws, and these documents may not be construed as doing so.

### Copyrights

IEEE draft and approved standards are copyrighted by IEEE under U.S. and international copyright laws. They are made available by IEEE and are adopted for a wide variety of both public and private uses. These include both use, by reference, in laws and regulations, and use in private self-regulation, standardization, and the promotion of engineering practices and methods. By making these documents available for use and adoption by public authorities and private users, IEEE does not waive any rights in copyright to the documents.

#### Photocopies

Subject to payment of the appropriate fee, IEEE will grant users a limited, non-exclusive license to photocopy portions of any individual standard for company or organizational internal use or individual, non-commercial use only. To arrange for payment of licensing fees, please contact Copyright Clearance Center, Customer Service, 222 Rosewood Drive, Danvers, MA 01923 USA; +1 978 750 8400. Permission to photocopy portions of any individual standard for educational classroom use can also be obtained through the Copyright Clearance Center.

### Updating of IEEE Standards documents

Users of IEEE Standards documents should be aware that these documents may be superseded at any time by the issuance of new editions or may be amended from time to time through the issuance of amendments, corrigenda, or errata. An official IEEE document at any point in time consists of the current edition of the document together with any amendments, corrigenda, or errata then in effect.

Every IEEE standard is subjected to review at least every ten years. When a document is more than ten years old and has not undergone a revision process, it is reasonable to conclude that its contents, although still of some value, do not wholly reflect the present state of the art. Users are cautioned to check to determine that they have the latest edition of any IEEE standard.

In order to determine whether a given document is the current edition and whether it has been amended through the issuance of amendments, corrigenda, or errata, visit the IEEE-SA Website at <u>http://ieeexplore.ieee.org/xpl/standards.jsp</u> or contact IEEE at the address listed previously. For more information about the IEEE-SA or IEEE's standards development process, visit the IEEE-SA Website at <u>http://standards.ieee.org.</u>

#### Errata

Errata, if any, for all IEEE standards can be accessed on the IEEE-SA Website at the following URL: <u>http://standards.ieee.org/findstds/errata/index.html</u>. Users are encouraged to check this URL for errata periodically.

#### Patents

Attention is called to the possibility that implementation of this standard may require use of subject matter covered by patent rights. By publication of this standard, no position is taken by the IEEE with respect to the existence or validity of any patent rights in connection therewith. If a patent holder or patent applicant has filed a statement of assurance via an Accepted Letter of Assurance, then the statement is listed on the IEEE-SA Website at <a href="http://standards.ieee.org/about/sasb/patcom/patents.html">http://standards.ieee.org/about/sasb/patcom/patents.html</a>. Letters of Assurance may indicate whether the Submitter is willing or unwilling to grant licenses under patent rights without compensation or under reasonable rates, with reasonable terms and conditions that are demonstrably free of any unfair discrimination to applicants desiring to obtain such licenses.

Essential Patent Claims may exist for which a Letter of Assurance has not been received. The IEEE is not responsible for identifying Essential Patent Claims for which a license may be required, for conducting inquiries into the legal validity or scope of Patents Claims, or determining whether any licensing terms or conditions provided in connection with submission of a Letter of Assurance, if any, or in any licensing agreements are reasonable or non-discriminatory. Users of this standard are expressly advised that determination of the validity of any patent rights, and the risk of infringement of such rights, is entirely their own responsibility. Further information may be obtained from the IEEE Standards Association.

#### **Participants**

At the time this IEEE standard was completed, the P2401 Working Group had the following membership:

Yoshinori Fukuba, Chair Yukio Masuko, Vice Chair

Takahiro Aoki Bradley Brim Norman Chang John Ellis Tadaaki Hitomi Hiroshi Ishikawa Takashi Otsuki John Park Herb Reiter Genichi Tanaka Atsushi Tomishima

The following members of the entity balloting committee voted on this standard. Balloters may have voted for approval, disapproval, or abstention.

Cadence Design Systems, Inc.

Japan Electronics and Information Technology Industries Association (JEITA) Marvell Semiconductor, Inc. Synopsys, Inc. Toshiba Corporation

When the IEEE-SA Standards Board approved this standard on 3 September 2015, it had the following membership:

John D. Kulick, Chair Jon Walter Rosdahl, Vice Chair Richard H. Hulett, Past Chair Konstantinos Karachalios, Secretary

Masayuki Ariyoshi Ted Burse Stephen Dukes Jean-Philippe Faure J. Travis Griffith Gary Hoffman Michael Janezic Joseph L. Keopfinger

\*Member Emeritus

David J. Law Hung Ling Andrew Myles T. W. Olsen Glenn Parsons Ronald C. Petersen Annette D. Reilly Stephen J. Shellhammer Adrian P. Stephens Yatin Trivedi Philip Winston Don Wright Yu Yuan Daidi Zhong

#### Introduction

This introduction is not part of IEEE Std 2401<sup>™</sup>-2015, IEEE Standard Format for LSI-Package-Board Interoperable Design.

To deal with the increasing difficulty of design and the cost competitiveness of the global market, and to shorten the development term, innovative design methodologies should be implemented. It has been difficult to achieve the optimization of an entire set of large-scale integrated (LSI) circuits, packages, and board (LPB) using individual design processes for each LPB part.

One possibility for optimization is to have a certain section design the whole LPB; however, gathering knowledge and integrating the design environment of each LPB part is difficult. Dedicated professional technicians of individual LPB parts, who have the best knowledge and performance of their own part's design tools, intend to create design optimization by having proper interoperable information exchanges among all LPB parties. In order to achieve a design that optimizes the balance between cost and performance, information about and the results of design should be well shared among cooperating LPB design sections.

The Japan Electronics and Information Technology Industries Association (JEITA) LPB Interoperable Design Process Working Group (LPB-WG) was established to identify the solution. The LPB-WG intends to make a standard for an exchange format to make it easy to exchange information between each of the LPB design departments, so that optimal design will be carried out quickly.

The LPB interoperable design process has the following issues:

- Netlist not unified on each LPB

- Complexity of the representation of the relationship as a whole arrangement of the LPB

- Differences in how to give the design constraints, lack of design information, and many discrepancies in design rules.

- Databases not unified in each LPB, or among different vendors

- No unified terms

Various problems caused by these issues include the following:

- A large effort is required for conversion of formats.

- The occurrence of conversion errors and connection errors is difficult to detect because there is a lack of the information needed to do so.

- It takes a long time to gather information, resulting in a long period of design and analysis.

- It is difficult to make optimal design changes because the entire verification process is difficult.

- EDA tool cost increase because of additional development required to support multiple formats.

- It is time-consuming for designers to communicate their intentions in a way that others understand.

Based on this analysis, the LPB-WG has established an interface format that can address these issues.

As the one of the case studies of the LPB interoperable design process, the power distribution network (PDN) should be designed with information about the other LPB parts to reduce the noise (see Figure i).

Reprinted with permission from JEITA.

#### Figure i—Power distribution network

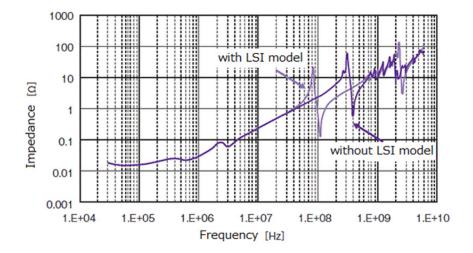

Resonance is caused by a capacitance and inductance present in the various parts in the LPB PDN. Impedance at the resonant frequency will be extremely large. If each part of the overall LPB design is not accurately simulated in the PDN model, the power supply circuit cannot be correctly designed (see Figure ii).

#### Figure ii—Example of PDN impedance

In order to run properly, this simulation should align a variety of information, such as the circuit model of power distribution network (PDN) of LSI, shape information about the package and board, electrical parameters of materials, and models of the components. It is difficult to make an efficient design when the specification or format of the design information is different in each part of the LPB, and the necessary parameters are not shared. When the format of the interface methods and models of the simulation are not consistent, the setup time and the cost of design/verification are enormous, which has become a barrier to cooperation in LPB design. The LPB-WG was established in JEITA to explore ways to create a mutual LPB interface to enable a more efficient co-design environment.

### Contents

| 1. Overview                                                                              | 1   |

|------------------------------------------------------------------------------------------|-----|

| 1.1 Scope                                                                                |     |

| 1.2 Purpose                                                                              |     |

| 1.3 Key characteristics of the LSI-Package-Board Format                                  |     |

| 1.4 Contents of this standard                                                            | 3   |

| 2. Normative references                                                                  | 2   |

| 2. Normative references                                                                  |     |

| 3. Definitions, acronyms, and abbreviations                                              |     |

| 3.1 Definitions                                                                          |     |

| 3.2 Acronyms and abbreviations                                                           | 6   |

|                                                                                          |     |

| 4. Concept of the LPB Format.                                                            |     |

| 4.1 Technical background                                                                 |     |

| <ul><li>4.2 Conventional design</li><li>4.3 Common problems at the design site</li></ul> |     |

| 4.5 Continion problems at the design site                                                |     |

| 4.4 Concept of LPB interoperable design                                                  |     |

| 4.5 Value creation by EFB interoperable design                                           |     |

| 4.7 Summary of LPB Format files                                                          |     |

|                                                                                          |     |

| 5. Language basics                                                                       | 16  |

|                                                                                          |     |

| 6. Common elements in M-Format, C-Format, and R-Format                                   |     |

| 6.1 General                                                                              |     |

| 6.2 The <header> element</header>                                                        |     |

| 6.3 The <global> element</global>                                                        | 19  |

| 7. M-Format                                                                              | 31  |

| 7.1 M-Format file structure                                                              |     |

| 7.2 The <include> element</include>                                                      |     |

| 7.3 The <class> element</class>                                                          |     |

|                                                                                          |     |

| 8. C-Format                                                                              |     |

| 8.1 C-Format file structure                                                              |     |

| 8.2 The <module> element</module>                                                        |     |

| 8.3 The <component> element</component>                                                  |     |

| 9 R-Format                                                                               | 86  |

| 9.1 R-Format file structure                                                              |     |

| 9.2 The <physicaldesign> element</physicaldesign>                                        |     |

| 9.3 The <constraintrule> element</constraintrule>                                        |     |

| 10 N Format                                                                              | 100 |

| 10. N-Format                                                                             |     |

| 10.1 Purpose of the N-Format file                                                        |     |

| 10.2 How to identify the power/ground network<br>10.3 Example                            |     |

|                                                                                          | 122 |

| 11. G-Format                                                                             |     |

| 11.1 Language basics of G-Format.                                                        |     |

| 11.2 Structure                                                                           |     |

| 11.3 Header section                                                                                                                                                                                                                                                                                     |     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 11.4 Material section                                                                                                                                                                                                                                                                                   |     |

| 11.5 Layer section                                                                                                                                                                                                                                                                                      |     |

| 11.6 Shape section                                                                                                                                                                                                                                                                                      |     |

| 11.7 Board geometry section                                                                                                                                                                                                                                                                             |     |

| 11.8 Padstack section                                                                                                                                                                                                                                                                                   |     |

| 11.9 Part section                                                                                                                                                                                                                                                                                       |     |

| 11.10 Component section                                                                                                                                                                                                                                                                                 |     |

| 11.11 Net attribute section                                                                                                                                                                                                                                                                             |     |

| 11.12 Netlist section                                                                                                                                                                                                                                                                                   |     |

| 11.13 Via section                                                                                                                                                                                                                                                                                       |     |

| 11.14 Bondwire section                                                                                                                                                                                                                                                                                  | 139 |

| 11.15 Route section                                                                                                                                                                                                                                                                                     | 141 |

|                                                                                                                                                                                                                                                                                                         |     |

| Annex A (informative) Bibliography                                                                                                                                                                                                                                                                      | 145 |

|                                                                                                                                                                                                                                                                                                         |     |

|                                                                                                                                                                                                                                                                                                         |     |

| Annex B (informative) Examples of utilization                                                                                                                                                                                                                                                           |     |

| B.1 Understanding the function of the LPB Format                                                                                                                                                                                                                                                        | 146 |

|                                                                                                                                                                                                                                                                                                         | 146 |

| <ul><li>B.1 Understanding the function of the LPB Format</li><li>B.2 Test bench</li><li>B.3 Design flow example</li></ul>                                                                                                                                                                               |     |

| B.1 Understanding the function of the LPB Format<br>B.2 Test bench                                                                                                                                                                                                                                      |     |

| <ul><li>B.1 Understanding the function of the LPB Format</li><li>B.2 Test bench</li><li>B.3 Design flow example</li></ul>                                                                                                                                                                               |     |

| <ul> <li>B.1 Understanding the function of the LPB Format</li> <li>B.2 Test bench</li> <li>B.3 Design flow example</li> <li>B.4 Growth of the sample files in the LPB Format</li> <li>B.5 Simulations using the sample files in the LPB Format</li> </ul>                                               |     |

| <ul> <li>B.1 Understanding the function of the LPB Format</li> <li>B.2 Test bench</li> <li>B.3 Design flow example</li> <li>B.4 Growth of the sample files in the LPB Format</li> </ul>                                                                                                                 |     |

| <ul> <li>B.1 Understanding the function of the LPB Format</li> <li>B.2 Test bench</li> <li>B.3 Design flow example</li> <li>B.4 Growth of the sample files in the LPB Format</li> <li>B.5 Simulations using the sample files in the LPB Format</li> <li>Annex C (informative) XML Encryption</li> </ul> |     |

| <ul> <li>B.1 Understanding the function of the LPB Format</li> <li>B.2 Test bench</li> <li>B.3 Design flow example</li> <li>B.4 Growth of the sample files in the LPB Format</li> <li>B.5 Simulations using the sample files in the LPB Format</li> </ul>                                               |     |

| <ul> <li>B.1 Understanding the function of the LPB Format</li></ul>                                                                                                                                                                                                                                     |     |

| <ul> <li>B.1 Understanding the function of the LPB Format</li></ul>                                                                                                                                                                                                                                     |     |

| <ul> <li>B.1 Understanding the function of the LPB Format</li></ul>                                                                                                                                                                                                                                     |     |

## IEEE Standard Format for LSI-Package-Board Interoperable Design

IMPORTANT NOTICE: IEEE Standards documents are not intended to ensure safety, security, health, or environmental protection, or ensure against interference with or from other devices or networks. Implementers of IEEE Standards documents are responsible for determining and complying with all appropriate safety, security, environmental, health, and interference protection practices and all applicable laws and regulations.

This IEEE document is made available for use subject to important notices and legal disclaimers. These notices and disclaimers appear in all publications containing this document and may be found under the heading "Important Notice" or "Important Notices and Disclaimers Concerning IEEE Documents." They can also be obtained on request from IEEE or viewed at http://standards.ieee.org/IPR/disclaimers.html.

#### 1. Overview

#### 1.1 Scope

This standard defines a common interoperable format that will be used for the design of a) large-scale integration (LSI), b) packages for such LSI, and c) printed circuit boards on which the packaged LSI are interconnected. Collectively, such designs are referred to as" LSI-Package-Board" (LPB) designs. The format provides a common way to specify information/data about the project management, netlists, components, design rules, and geometries used in LPB designs.

#### 1.2 Purpose

The general purpose of this standard is to develop a common format that LPB design tools can use to exchange information/data seamlessly, as opposed to having to work with multiple different input and output formats.

#### 1.3 Key characteristics of the LSI-Package-Board Format

LPB format will facilitate the exchange of design information. This functionality provides the ability to plan the entire design at an early stage. In effect, post-design analysis will be possible throughout the entire